1. Fabless、Foundry、IDM

半导体行业根据生产设计以及制造能力分为不同的公司种类,分别是Fabless, Foundry和IDM。

- Fabless

Fabless 指的只从事芯片设计与销售,不从事生产的公司,这样的企业被成为“无厂化企业”,手机厂商中的华为、苹果和小米,还有高通和联发科,都属于 Fabless。

目前大多数的芯片公司基本都是Fabless,也就是大家只负责芯片的开发设计,然后生产可以找专业的代工厂进行生产。芯片的开发设计是一个需要大量人力进行创新的领域,相对于生产设计投入成本相对较小,但是收益周期会更快。因此更多的公司只会选择开发设计这一块来做。

- Foundry

Foundry 是能够自行完成芯片制造,但是没有设计能力的厂商,就是我们所熟知的代工厂。台积电就是典型的 Foundry,专注芯片制造,发展相关的工艺和制程,所以 Foundry 厂商其实就是 Fabless 厂商的代工方。

- IDM

IDM 就是指既能够自行设计、也能够自行生产的芯片厂商,世界上有这种能力的不多,三星和英特尔。

2. 半导体集成电路和晶圆有何关系?

半导体集成电路是将很多元件集成到一个芯片内, 以处理和储存各种功能的电子部件。

晶圆是指将硅(Si)、砷化镓(GaAs)等生成的单 晶柱切成薄片的圆盘。大部分晶圆都是由沙子中提 取的硅制成的。地球上有大量的硅,可以稳定供应, 并且硅具有无毒、环保的特点。

由于半导体集成电路是通过在晶圆的薄基板上制造多个相同电路而产生的, 因此晶圆是半导体的基础, 就像盖房子打地基一样。

3. 半导体晶圆制造工艺

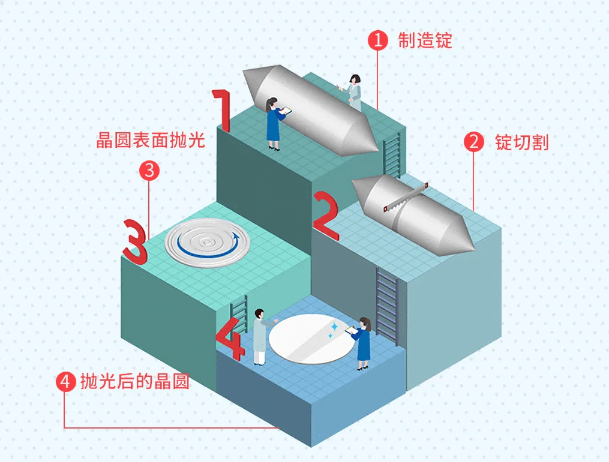

第一阶段

制造锭(Ingot)

为了将从沙子中提取的硅作为半导体材料使 用,首先需要经过提高纯度的提纯工序。将硅 原料高温溶解,制造高纯度的硅溶液,并使其 结晶凝固。这样形成的硅柱叫做锭(Ingot)。 用于半导体中的锭采用了数纳米(nm)微细 工艺,是超高纯度的硅锭。

第二阶段

绽切割成薄晶圆(Wafer Slicing)

为了将圆陀螺模样的镜制成圆盘状的晶圆,需 要使用金刚石锯将其切成均匀厚度的薄片。 的直径决定了晶圆的尺寸。晶圆的尺寸有 150mm(6英寸)、200mm(8 英寸)、300mm (12 英寸)等等。晶圆越薄,制造成本越低, 直径越大,一次可生产的半导体芯片数量就越 多,因此圆的厚度和大小呈逐渐变薄和扩大的 趋势。

第三阶段

晶圆表面抛光 (Lapping&Polishing)

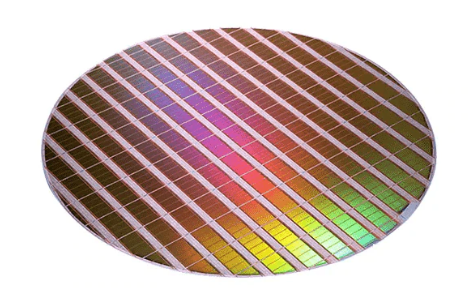

切割后的晶圆需要进行加工,以使其像镜子一 样光滑。这是因为刚切割后的晶圆表面有瑕疵 且粗糙,可能会影响电路的精密度,因此需要 使用抛光液和抛光设备将晶圆表面研磨光滑。 加工前的晶圆就像处于没有穿衣服的状态一 样,所以叫做裸晶圆(Bare wafer)。经过物理、 化学多个阶段的加工后,可以在表面形成 IC。 经过加工阶段后,会成为如下形状。

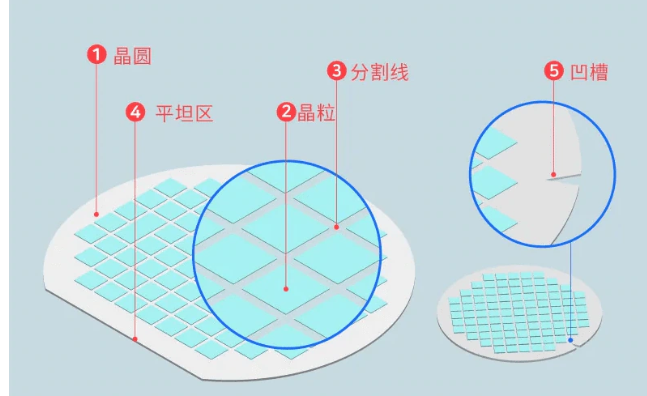

4. 晶圆各个区域

晶圆(Wafer): 晶圆圆是半导体集成电路的核心材料,是一种圆形的板。

晶粒(Die): 很多四边形都聚集在圆形晶圆上。 这些四边形都是集成电子电路的 IC芯片。

分割线(Scribe Line): 看上去各个晶粒像是 粘在一起,但实际上晶粒和晶粒之间具有一定的间隙。该间距称为分割线。在晶粒和晶粒之间设 置分割线的是为了在晶圆加工完成后将这些晶粒一个个割断,然后组装成芯片,也是为了留出用金刚石锯切割的空间。

平坦区(Flat Zone): 平坦区是为区分晶圆结 构而创建的区域,是晶圆加工的标准线。由于晶圆的晶体结构非常精细并且无法用肉眼判断,因 此以这个平坦区为标准来判断晶圆的垂直和水平。

凹槽(Notch): 如今也出现了具有凹槽的晶 圆。和平坦区晶圆相比,凹槽晶圆可以制造更多的晶粒,因此效率很高。

半导体产业包括生产晶圆的晶圆产业以及以晶圆为材料设计和制造的晶圆加工产业——制造行业 (Fabrication, FAB)。另外,还有组装产业,它将 加工过的晶圆切割成晶粒,并包装好以防止受潮或受压。

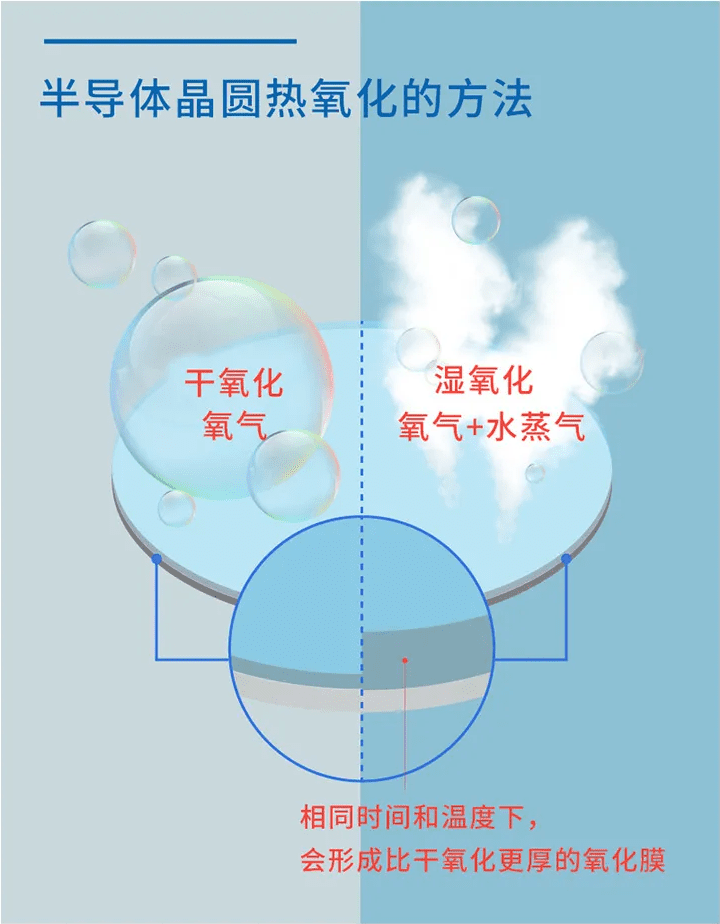

5. 保护晶圆表面的氧化工艺

晶圆的保护膜和绝缘膜是“氧化膜”(二氧化硅,SiO2)

晶圆的保护膜和绝缘膜是“氧化膜”(二氧化硅,SiO2) 为了将从沙子中提取的硅作为半导体集成电路的原材 料,需要对其进行一系列的提纯,才可制造出称为锭(Ingot)的硅柱,然后将该硅柱切成均匀的厚度,经 过研磨后,制成半导体的基础——晶圆。 这样所制成的薄而圆的晶圆是不导电的绝缘体,因此 有必要制作同时具有导体和绝缘体性质的“半导体”。 为此,需要在晶圆上形成各种物质后,按照设计好的 电路形状进行切割,重复之前步骤,再形成物质,然 后进行切割。

当晶圆暴露在大气中或化学物质中的氧气时就 会形成氧化膜。这与铁(Fe)暴露在大气时会氧化生锈是一样的道理。 可以在晶圆上形成薄膜的氧化工艺方式有通过 热进行的热氧化(Thermal Oxidation),等离子 体增强化学气相沉积法(Plasma Enhanced Chemical Vapor Deposition, PECVD)和电化 学阳极氧化等等。其中,最常用的方法是热氧化 法,即在800~1200°C的高温下形成一层薄而均 匀的硅氧化膜。 根据氧化反应所使用的气体,热氧化法可分为干 氧化(Dry Oxidation)和湿氧化(Wet Oxidation)。干氧化只使用纯氧气(O2),所以氧 化膜的生长速度较慢,主要用于形成薄膜,且可形成具有良好导电性的氧化物。湿氧化同时使用氧气(O2)和高溶解性的水蒸气(H2O)。所以,氧化膜生长速度快,会形成较厚的膜。但与干氧化相比,湿氧化形成的氧化层密度低。通常,在相同 温度和时间下,通过湿氧化获得的氧化膜比使用干氧化获得的氧化膜要厚大约5至10倍。

5. 晶圆上绘制电路的光刻工艺

光刻工艺类似于洗印黑白照片

人们经常将 Photo Lithography(光刻)缩写成 Photo。得此名称的原因是,这个工艺在晶 圆上利用光线来照射带有电路图形的光罩,从而绘制电路。形成图形的方法类似于在洗印黑 白照片时,将在胶片上形成的图像印在相纸上。 随着半导体集成度的提高,构成芯片的单元元 件也要使用微工艺做得更小。由于微电路图形 的实现也全由光刻工艺决定,因此集成度越高, 光刻工艺技术就越需要更精细和更高级的技术。

晶圆电路图形制造准备阶段

那么我们开始正式了解一下光刻工艺是如何进 行的吧!首先,使用电脑系统设计(计算机辅助设计, CAD, computer-aided design)将要在晶圆上绘制的电路。依照电路图形(Pattern)所设计的图中包含工程师设计的精密电路,其精密度决定半导体的集成度。

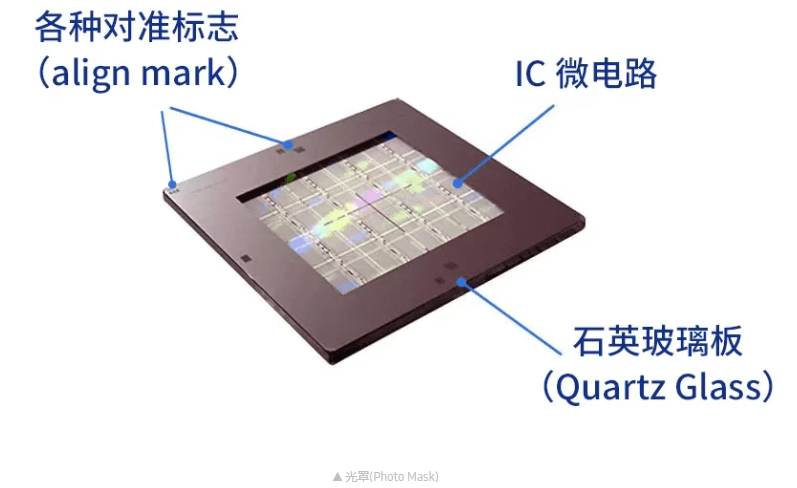

制造具有照片底片一样作用的光罩

设计好的电路图形通过在由高纯度石英加工而 成的基板上形成含铬(Cr)的微电路,从而成 为光罩。光罩也称为掩膜,相当于可以反映电路模图形的胶卷,具有照片底片的功能。为了形成更精细的图形(Patterning),光罩比半导 体电路制作的更大,并且利用透镜减来少光的 照射。 光刻工艺可以细分为涂胶、曝光、显影。

氧化膜的形成方法

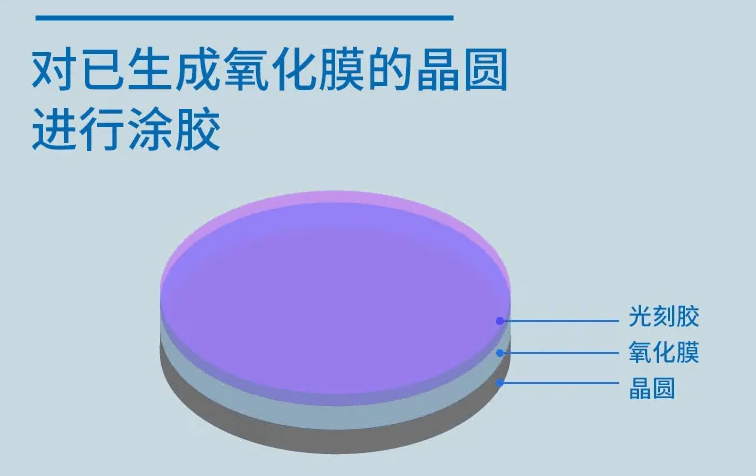

现在在晶圆上作画的准备工作已完成。下一步 是在晶圆表面均匀涂抹对光敏感的物质——光刻 胶(PR, Photo Resist)。这就像冲洗照片一样, 是将晶圆变成相纸的过程。为了获得更高质量的微电路图形,光刻胶(PR)膜必须薄且均匀,且对光要具有高度敏感性。

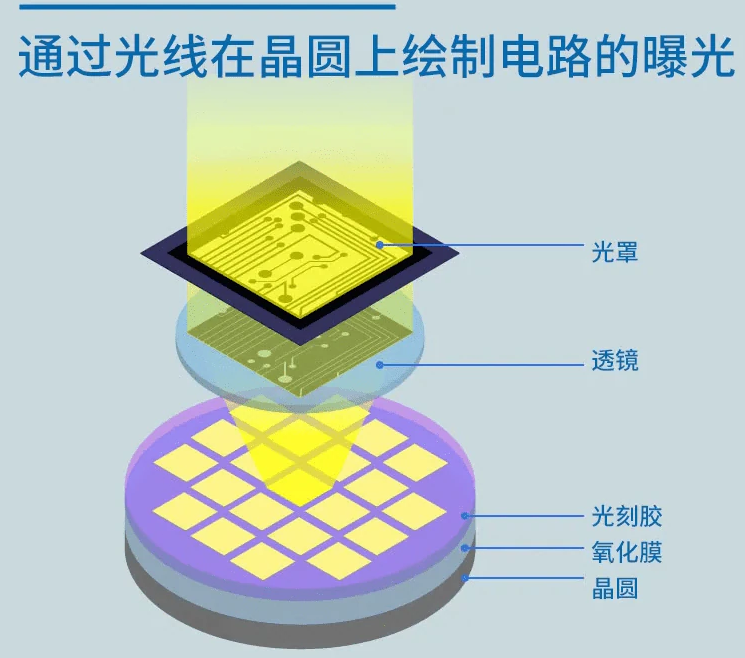

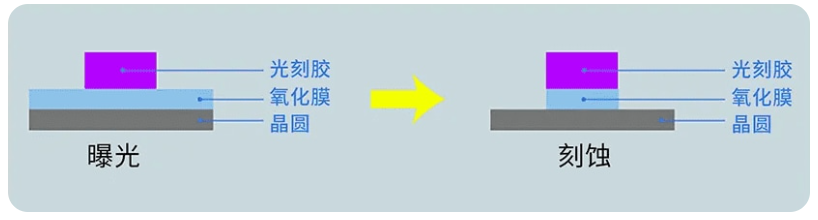

通过光线在晶圆上绘制电路的曝光

通过涂胶工序,形成光刻胶(PR)膜,使晶圆成为类似于相纸 的状态后,使用曝光设备(步进式光 刻机,Steper)使光穿过包含电路图形的光罩,将电路印在晶圆上。这个过程叫做“曝光”(Steper Exposure)。半导体工艺中的曝光是指 选择性地照射光的工序。

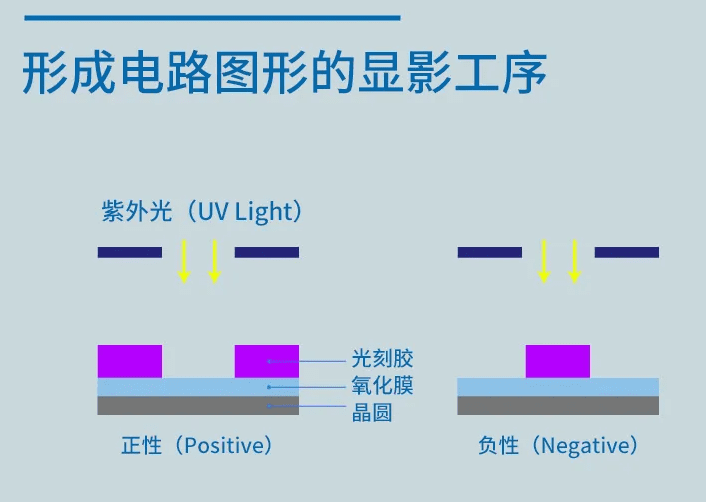

光刻工艺的最后一个阶段是显影(Develop),与 照片的显影过程一样。显影过程决定图形的形 成,所以非常重要。显影(Develop) 是在晶圆上 喷洒显影液后,选择性的去除曝光区和非曝光 区,从而形成电路图形的工序。 均匀涂抹在晶圆上的光刻胶(PR)根据其对光的 反应方式分为正性(positive)或负性 (negative)。在正性光刻胶的情况下,留下未曝 光的区域,而在负性光刻胶的情况下,仅使用曝光的区域。 显影过程结束后,光刻工艺就完成了。在用各种测量设备和光学显微镜仔细检查图形是否绘制好之后,只有完成这些工序的晶圆才能进入下一 个工程阶段。

6. 半导体电路图形的完成 -“刻蚀工艺”

大家在学生时代的美术课上创作过的“版画”是一种通过在木材、金属或石材的表面上绘制形状,然后涂上墨水或颜料印在纸或布上的绘 画形式。刻蚀工艺与这种版画的刻蚀 (Etching)技术有着相似的原理。 绘画中的刻蚀技术是指在銅板上涂抹防止酸产 生化学反应的防腐蚀剂,然后利用锋利的工具 刮削,露出铜板的过程,然后再将铜板放入腐 蚀液(稀硝酸)中,控制其腐蚀程度从而产生图形。

干法刻蚀过程中的注意事项

第一,维持一致性(Uniformity)。一致性是指刻 蚀的速度在晶圆上的各个部位“有多相同”在 工艺进行的过程中,一定时间下,不同的晶圆部位刻蚀的速度不同,形成的形状也可能不同,所以可能会导致位于某些部位的芯片发生不良现象或其特性发生变化。 第二,刻蚀速度(Etch Rate)。它意味着在一定时间内可以去除多少薄膜。刻蚀速度主要取决于表面反应所必需的反应性原子和离子的数量以及离子的能量,所以提高对这些因素的控制能力就可以提高总收益率。此外,选择性(Selectivity)、形状(Profile)等也是干式刻蚀的重要因素。

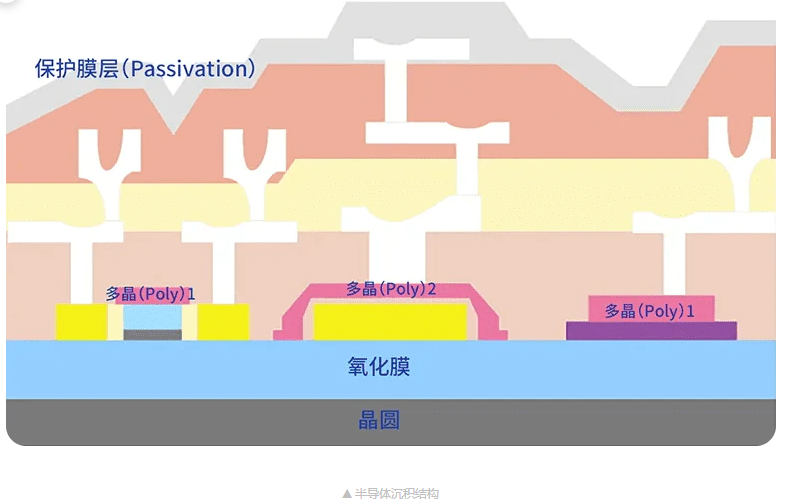

7. 沉积&离子注入工艺使半导体具有电特性

在比人类的“指甲盖”还小、像纸一样薄的半导 体芯片上,有着细小的、数以“百万计”的层 (layer)。就像高楼大厦一样高而坚固地堆叠起来, 构成复杂的结构。 为了形成这种结构,在半导体原材料的单晶硅 (Si)晶圆上逐步涂上薄膜,通过绘制电路的光刻 工艺,反复进行有选择地去除不必要部分的蚀刻 和清洗过程。 这时,起到电路之间的分隔、连接和保护作用的称为薄膜(Thin film)。

给晶圆穿上薄衣的沉积工艺(deposition)

词典中的“薄膜(thin film)”是指仅靠机械加工 无法实现的在1微米(um,百万分之一米)以下 的薄膜。在晶圆上加入所需分子或原子单位薄膜 的一系列过程叫做沉积(Deposition)。由于厚度 本来就薄,为了在晶圆上均匀地形成薄膜,需要 精巧、细致的技术。

沉积的方法大致分为两种,物理气相沉积方法 (Physical Vapor Deposition, PVD)和化学气相 沉积方法(Chemical Vapor Deposition, CVD)。

物理气相沉积法主要用于金属薄膜的沉积,不会产生化学反应。化学气相沉积法是通过以蒸气态或气态的气体与外部能量发生化学反应,从而形 成沉积的方法。该技术可用于导体、绝缘体和半导体的薄膜沉积。

目前,半导体工艺主要使用的是化学气相沉积法。根据所使用的外部能量不同,化学气相沉积可分为热化学气相沉积(thermal chemical vapor deposition, TCVD),等离子体化学气相 沉积(plasma chemical vapor deposition, PCVD)和光化学气相沉积(photo chemical vapor deposition, Photo-CVD)。由于等离子体 化学气相沉积可以在低温下形成,可控制使其厚度均匀,且可大规模加工,因此被广泛使用。 通过沉积工艺形成的薄膜大致分为连接电路间 电信号的金属膜(导电)层和电气分离内部连接 层或切断污染源头的绝缘膜层。

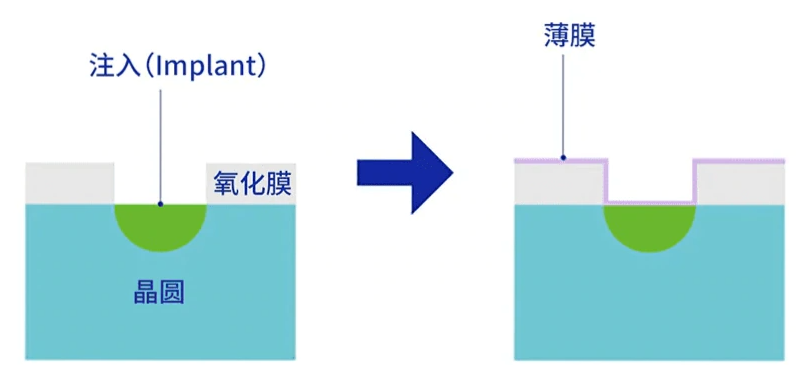

将晶圆转化为半导体的离子注入工程(lon Implantation)

此时,需要可以使半导体具有电特性的工艺。在同时具有导电的导体和不导电的绝缘体的特性 的半导体中,离子注入工艺(lon Implantation)是给硅晶片注入半导体的生命 的过程。纯半导体由硅素制成,因此它们不能导电,但通过添加杂质,可以使其电流流动,具有导电性。

此时将杂质称为离子(ION),将离子变成微小的气体粒子,均匀地放入晶圆的表面,使其达到想要的深度。这里使用杂质有 15 族元素磷(P)、 砷(As)和 13 族元素硼(B)等。如果加入15 族 元素,就会成为n型半导体;如果加入 13 族 元素,就会成为p型半导体。

薄膜的厚度和均匀程度决定半导体的质量,所 以沉积工艺非常重要。未来,为了让只有数百万 分之一头发丝大小的半导体电路结构具有电特 性,需要采用使薄膜更薄、更均匀的沉积技术。

7. 连接电路的金属布线工艺

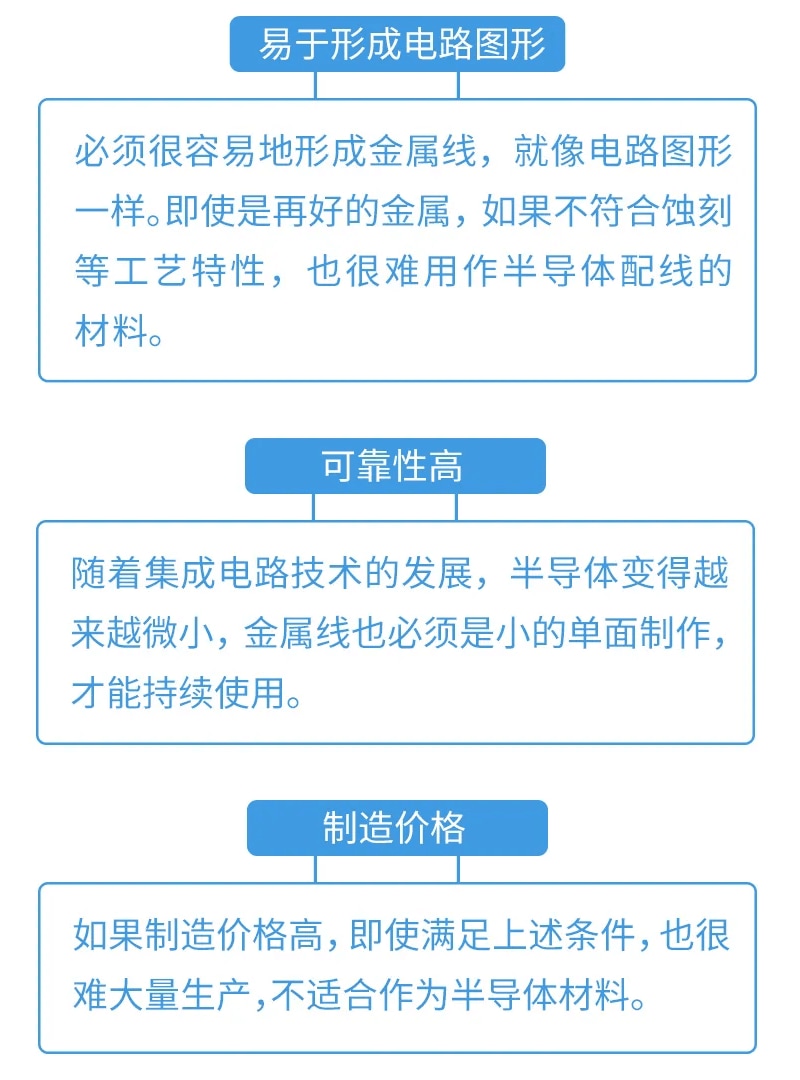

半导体具有导电的“导体”和不导电的“绝缘体” 的特性。在纯硅中加入杂质的离子注入工艺 (lon Implantation)使具有导电性的半导体可以根据需要调节电流是否流动。 反复进行光刻,蚀刻,离子注入和沉积工艺,会 在晶圆上形成大量的半导体电路。电路正常运行需要来自外部的电脉冲,为了保证顺利传输信号,根据半导体电路图连接电路(金属线)的过程,称为金属布线工艺。

满足以上条件且具有代表性的金属有铝(Al)、 (Ti)、钨(W)等等。那么,金属布线工艺是如何完 成的呢?

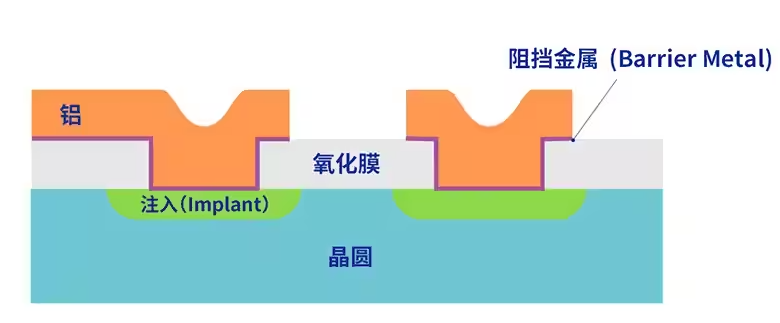

铝是具有代表性的半导体用金属配线材料,是因 为它可加工性强,与氧化膜(二氧化硅, Silicon Dixide)的粘附性好。 但是,当铝(Ai)与硅(Si)相遇时,会相互混合。因 此,对于硅晶圆来说,在铝接线过程中会出现接 合面被破坏的现象。为了防止这种情况的发生, 在铝和晶圓接合面之间进行沉积,增加起到阻挡 (Barrier)作用的金属,称为阻挡金属(Barrier Metal)。这样形成双层薄膜后,可以防止接合面被破坏。 金属布线也是通过沉积完成的。将金属放入真空 室(Chamber)中,在低压下煮沸或电击时,金属 就会变成蒸气状态。这时,将晶圆放入真空室中,就会形成金属薄膜。 日益精细化的半导体工艺,通过不懈的研发,不断发生着变化。在金属布线工艺中,也正向化学 气相沉积(CVD)过渡。

8. EDS工艺

经过大量制造工序的半导体芯片,还需要通过最后一个工艺的测试,筛选出不合格与合格产 品。在半导体制造过程中,会进行各种测试。 晶圆完成阶段的EDS 工艺(Electrical Die Sorting),组装工艺和封装工(Pakaging), 还有产品出厂前从消费者的角度进行的质量测试等。

直接关系到半导体产量提高的EDS工艺

EDS 工艺(Electrical Die Sorting)在晶圆上 绘制电路的制造工艺(Fabrication, FAB)与 最终形成产品的封装工艺之间进行。其目的如下所示: • 通过电气特性检测,确定各个芯片是否达到所需的质量水平 • 对晶圆状态的半导体芯片进行筛选,选出不合格与合格产品 • 在不合格芯片中选出可修补的芯片,使其合格化 • 修正制造过程或设计中发现的问题 • 通过提前筛选出不合格的芯片,来提高后续封装和测试工作的效率

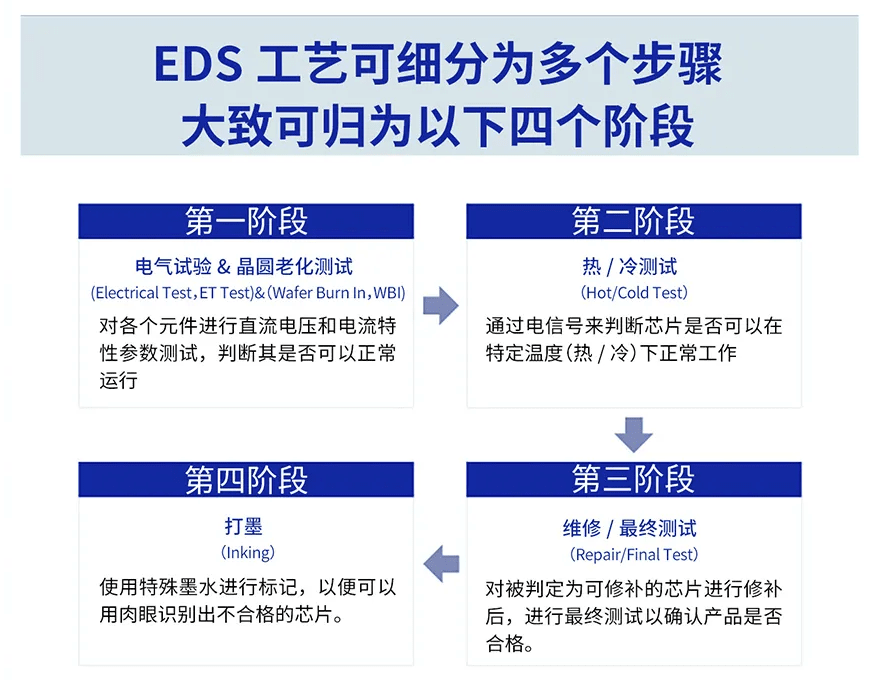

EDS工艺的4个阶段

第1阶段 - 电气试验(Electrical Test, ET Test)和晶圆老化测试(Wafer Burn In, WBI) 电气试验是对半导体集成电路(IC)操作所需的各个元件(晶体管,电阻,电容器,二极管)进行直流电压和电流特性参数测试,判断其是否可以正常运行的过程。可以说这是对半导体芯片(Chip)进行 的首次测试。 晶圆老化测试工序是通过将晶圆加热到一定温度,施加交流(AC)/ 直流(DC) 电压后,找出产品组合或薄弱部分等潜在的不合格因素,以有效提高产品可靠性的过程。

第2阶段 - 热/冷测试(Hot/Cold Test) 热/冷测试是通过电信号来检查晶圆上的每个芯片 是否有缺陷的过程。可以修补的芯片会保存信息,以便进行修补处理。此测试是通过进行高于常温、 低于常温的测试,来确定芯片在特定温度下是否可以正常工作。

第3阶段 - 维修(Repair) / 最终测试(Final Test) 维修过程是 EDS 工艺中最重要的阶段。 在维修过程中,首先对在热/冷工序中被判定为可 修补的芯片进行修补。在修补完成后,进行最终测试,再次验证是否已经修补完成,以最终确认产品是否合格。

第4阶段 - 打墨(Inking) 打墨是指在不合格的芯片上印上特殊墨水,以便可以用肉眼识别出的过程。它用于区分在热/冷测试过程中被判断为不合格的芯片,在最终测试过程中再次验证为不合格的芯片以及未在晶圆中完成的半导体芯片(Dummy Die)等。过去的打墨是将墨水直接涂印在有缺陷的芯片上。但是现在,仅通过数 据(Data)就可以分辨出芯片是否合格。这些被检 测为不合格的芯片不会进行封装,因此可以减少在 封装和检测工艺中使用的原材料、辅助材料、设备、 时间、人员等的损失。

打墨完成后,将晶圆进行干燥(Bake),然后通过质 量控制(Quality Control, QC)检测,将被转移到 封装工艺中。